Intel объявляет о выпуске FPGA серии Agilex 7 M-Series с поддержкой R-Tile, PCIe 5.0 и CXL 2.0

Сегодня Intel повышает планку, анонсируя семейство Field-Programmable Gate Array (FPGA) Agilex 7 M-Series, используя их передовой 10-нанометровый процесс SuperFin.

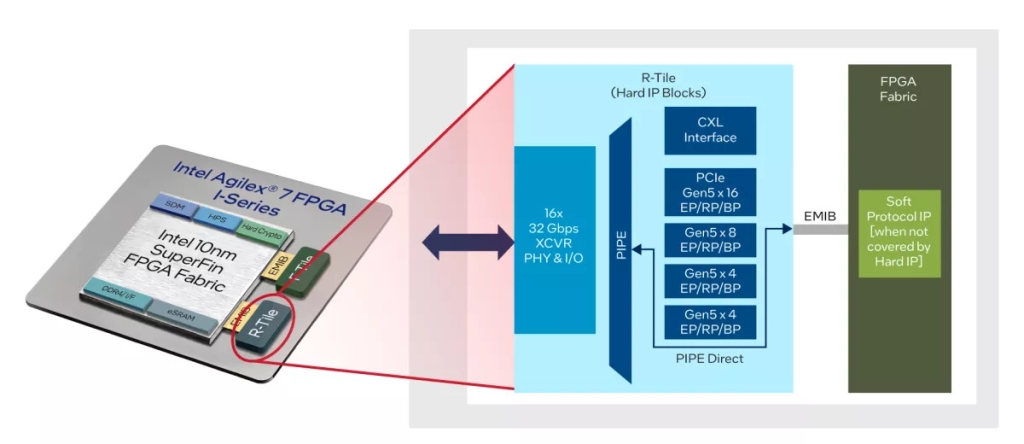

По мере того как рыночный спрос на решения FPGA в качестве сопроцессоров в сетевых системах, дата-центрах, высокопроизводительных вычислениях, облачных вычислениях и других областях продолжает расти, Intel готова предоставить беспрецедентную масштабируемость и адаптивность, результат которых – программируемая природа FPGA. FPGA Agilex 7 представляют новый чиплет, R-Tile, который является неотъемлемой частью их разнообразной многокристальной архитектуры и разработан для предложения передовых технологий связи, таких как PCIe 5.0 и CXL с помощью аппаратно-ускоренных, жестко закодированных IP-блоков.

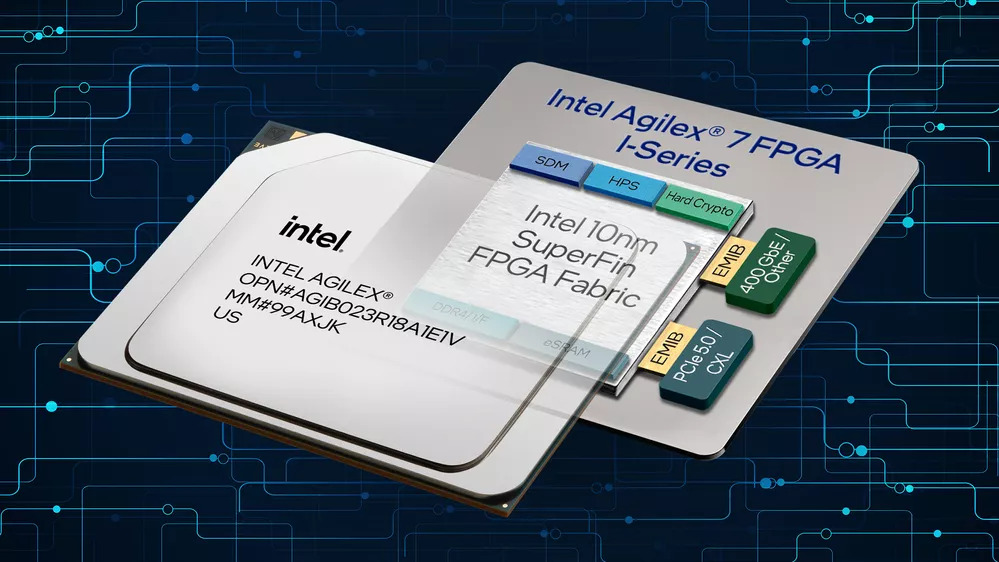

FPGA Agilex 7 производятся с использованием технологии 10nm SuperFin от Intel, собирая ряд различных IP-блоков на интерпозере, которые связаны через EMIB от Intel. Новый чиплет R-Tile, включающий свои возможности PCIe 5.0 и CXL 2.0, заключен в одиночный чиплет. (Фото: Intel Corporation)

Новый чиплет R-Tile - это прорывное новшество для Intel, что позволяет ей заявить о себе как единственной семье FPGA, которая имеет сертификацию полной скорости передачи данных PCI-SIG 5.0 x16. Это ставит Intel впереди других передовых разработчиков FPGA, таких, как Xilinx, который теперь является частью AMD.

Интересно, что Intel, по-видимому, удваивает разделение между продуктами FPGA и CPU. Возможно, это результат ее ранних попыток интеграции, которые не дали ожидаемых результатов. С другой стороны, AMD, по-видимому, планирует интегрировать возможности FPGA в свои процессоры EPYC возможно уже в этом году.

FPGA, благодаря своей внутренней гибкости, позволяют разработчикам быстро настраивать схемы и блоки обработки для адаптации FPGA под конкретные нагрузки. Будучи более специализированным оборудованием, FPGA могут быть использованы для ускорения нагрузок, которые не зависят от CPU, освобождая ресурсы CPU для выполнения специфических задач и тем самым повышая энергетическую эффективность.

R-Tile от Intel вносит аппаратно-ускоренные IP-блоки, отвечающие за управление протоколами PCIe 5.0 и CXL 1.1/2.0, в семейство FPGA Agilex 7. От этого ожидается повышение энергетической эффективности и пропускной способности данных, что снижает общую стоимость владения (TCO) для высокопроизводительных установок.

R-Tile направлен на уменьшение нагрузки на CPU при повышении производительности. Однако альтернативное решение может быть увеличение количества доступных ресурсов CPU. Это может быть достигнуто с помощью большего количества CPU или дополнительных ядер CPU.

Введение Agilex 7 символизирует уверенность Intel в своем понимании потребностей рынка: уменьшить нагрузку на CPU, переключив её на упаковку FPGA. Этот переход также выгоден для Intel с точки зрения собственной эффективности и снижения затрат.

Здесь реально проявляет себя встроенный мост между многочиповыми интерконнектами Intel (EMIB). Выступая в качестве связующего звена для различных блоков обработки, EMIB позволяет Intel дальше отделять IP-блоки на уровне производства, тем самым увеличивая эффективность кристалла и снижая стоимость на вафельный уровень.

С точки зрения потребителя, это потенциально снижает затраты. В идеале клиенты смогли бы выбирать и комбинировать различные блоки оборудования IP в соответствии с их конкретными потребностями, таким образом, платя только за те компоненты, которые они действительно будут использовать. В сущности это сделало бы каждую микросхему FPGA.

В заключении, Agilex 7 с R-Tile не только представляет собой новый продукт FPGA, но и символизирует новое добавление к предложению услуг Intel Foundry Services (IFS). В любом случае это укрепляет позиции Intel в том направлении, которое ей необходимо двигаться. И это просто хороший бизнес.

- Комментарии